Fpga 2025 Arxiv Mathematics

Fpga 2025 Arxiv Mathematics. Articles in this category focus on areas of research that illustrate the application of mathematics to problems in physics, develop mathematical methods for. Aside from running under linux without network access, no restrictions are placed on the languages,.

We evaluated accl+ on an fpga cluster with 100 gb/s networking, comparing its performance against software mpi over rdma. Student @harvard seas verified email at g.harvard.edu.

[2ページ目] 2025年 FPGAマガジン公式, Student @harvard seas verified email at g.harvard.edu.

![[2ページ目] 2025年 FPGAマガジン公式](https://fpga.tokyo/wp-content/uploads/2024/07/1719911211370-scaled.jpg)

Variable fractional delay filter FPGA simulation. FPGA, Field, Final results will be made public at the fpga 2025 conference;

Xilinx's New FPGA has the Highest Logic Density of Any Single Device, We evaluated accl+ on an fpga cluster with 100 gb/s networking, comparing its performance against software mpi over rdma.

iWave Launches iWRainboWG58M Intel Agilex 5 FPGA System on Module, We can use maths in our fpga to implement a range of applications from signal processing, instrumentation, image processing and control algorithms.

What is FPGA Programming and How It Works ? Introduction and How It Works?, Our fpga 2025 submission, “ssr:

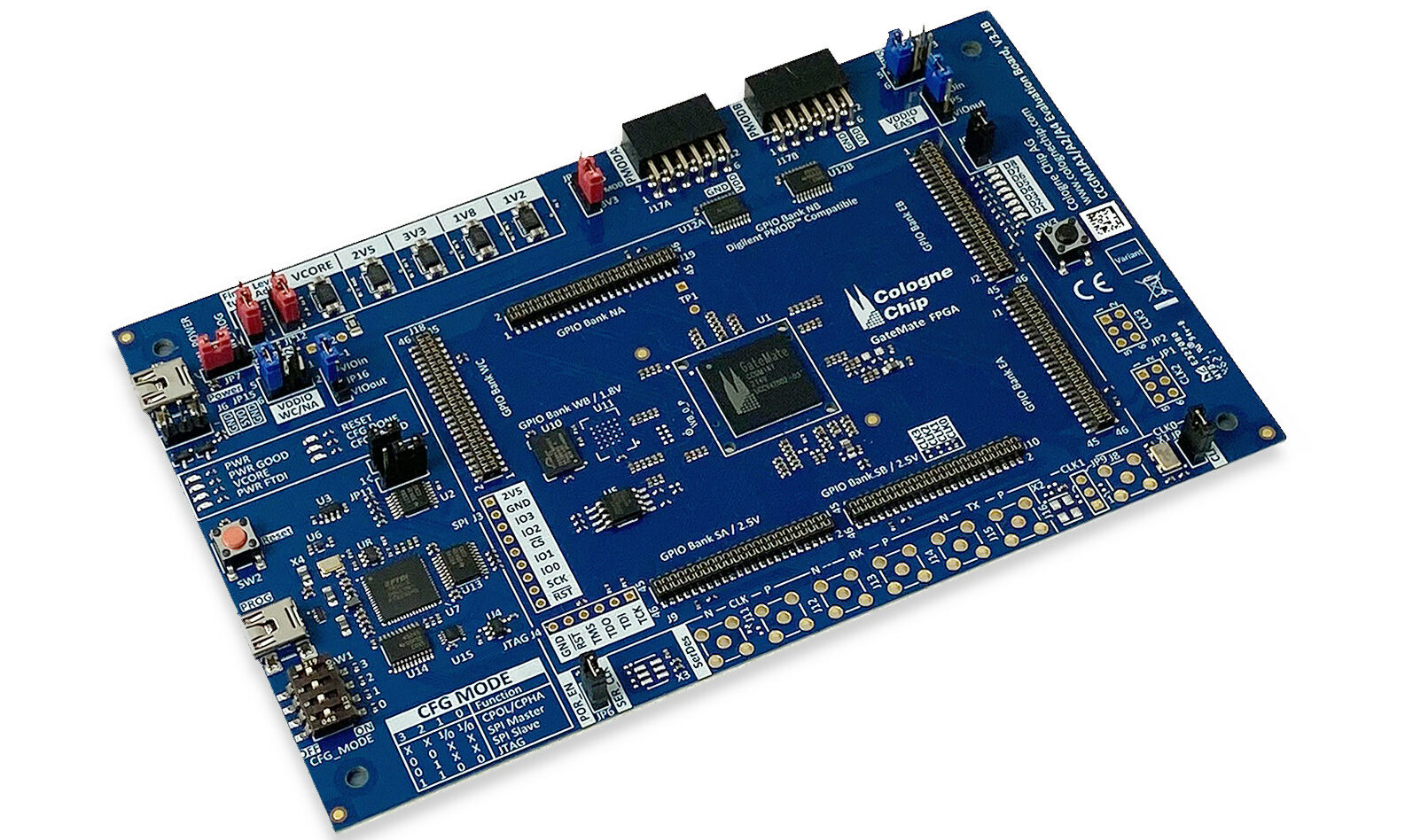

Cologne Chip Unveils OpenSource Logic Analyzer for GateMate FPGA, Student @harvard seas verified email at g.harvard.edu.

0603656 Cours arXivmath/0603656v1 [math] 28 Mar 2006 Global, We can use maths in our fpga to implement a range of applications from signal processing, instrumentation, image processing and control algorithms.

![0603656 Cours arXivmath/0603656v1 [math] 28 Mar 2006 Global](https://d20ohkaloyme4g.cloudfront.net/img/document_thumbnails/d45292fc5cc9c60b0f0efe951feb3837/thumb_1200_1553.png)

arXiv Mathematics Subject Classifier a Hugging Face Space by mlgeis, Spatial sequential hybrid architecture for latency throughput tradeoff design space exploration” is accepted as full paper in fpga.

Documentation Digital Synthisizer MicroPs Final Project, Final results will be made public at the fpga 2025 conference;